- 2021/2/25 14:50:53

- 类型:原创

- 来源:电脑报

- 报纸编辑:电脑报

- 作者:电脑报

01

台积电3nm工艺或于2年内准备就绪

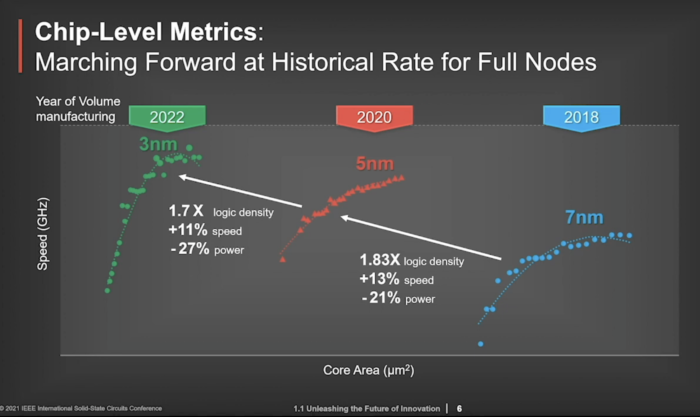

台积电董事长刘德音(Dr. Mark Liu)证实,该公司的下一代 3nm 芯片制造节点,正在按计划推进之中。作为全球知名的芯片代工制造商,台积电当前正在建设 3nm 生产线,且有望明年转入试生产。与 5nm 制程节点相比,3nm 可提供几乎翻番的逻辑密度,辅以 11% 的性能提升、或 27% 的能效改进。

3nm较5nm制程的增益示例(图 via WCCFTech)

积电高管在早前的国际固态电路会议(ISSCC)演讲期间的这番表态,证实了该公司对下一代制造技术的信心。

在满足当前和未来产品的日益增长需求的同时,即便汽车领域的产品需求有所提升,也不会对整体产能造成太大影响。

需要指出的是,部分媒体误解了所谓的“3nm 工艺提前”。毕竟在主题为《释放创新未来》的 27 分钟演讲期间,高管并未直言此事,仅在开头和结尾对 3nm 开发进度“顺口一提”。

为提升逻辑密度,需要对相关技术展开协同优化,同时也增加了一定的成本。

除了透露 3nm 技术的发展正在如期推进且相当顺利,刘德音还提供了对 3nm 工艺的最新数据、以及对工艺发展的看法。

他指出,到目前为止,台积电已出货约 18 亿片基于 7nm 工艺节点的芯片。截止 2020 年,该公司一直是行业中的领跑者。

得益于极紫外光刻(EUV)技术,台积电能够实现更高的保真度、缩短周期、并降低工艺的复杂性和缺陷率。

值得一提的是,台积电在 5nm 节点的十层掩模工艺中使用了 EUV 技术(具体包括线切割、接触、金属线图案),并用单层 EUV 取代了早期的多层深紫外(DUV)工艺。

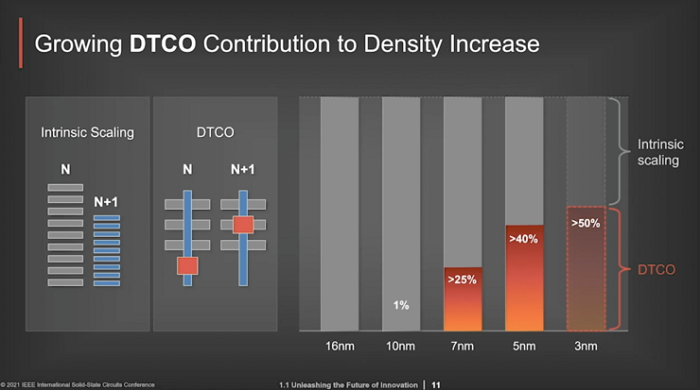

随后刘德音强调了设计技术的协同优化(DTC),以及该方案在过去几年中对芯片制造的重要性。对于芯片制造商来说,这使得他们能够同时使用设计和制造技术来满足性能要求。

此外 DTCO 使得台积电在衡量节点的逻辑密度时超越了固有的缩放指标,比如接触栅间距和最小金属间距。

结合有源区上的栅极接触、单扩散中断、鳍片减少等特性,还可为 3nm 工艺节点带来 1.8 倍于 5nm 的逻辑密度。

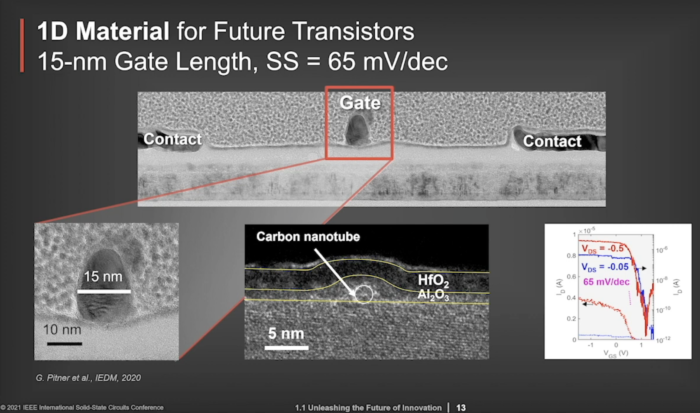

最后,刘德音披露了公司的未来计划,包括开发 sub-3D 材料和晶圆级单晶六方氮化硼。

两者的特点是能够在较低的制造温度下,转移至任意衬底上,从而为在三个维度上制造有源逻辑层和存储层开辟了新的道路。

此外台积电对于低维材料的研究,包包括一维的碳纳米管。借助这一晶体通道的关键,是开发出一种栅极长度较短的晶体管介电材料。

如上图所示,研究表明这项技术已有实现的可能。具有高k栅极堆叠能力的新材料,很适合用于制造栅极长度为 10nm 的晶体管。

当然,为了达成如此远大的目标,台积电还需要与芯片行业的所有同行紧密合作,以确保 3nm 工艺能够发展到 2 倍于当前的性能。

考虑到该公司正在量产的 5nm 顺应了这一趋势,即将面世的 3nm 节点也有望遵循这一时间安排。

02

三星去年12月领先台积电

台积电如此积极地推动技术革新,恐怕与三星去年12月领先台积电成为全球头号晶圆制造商有关。

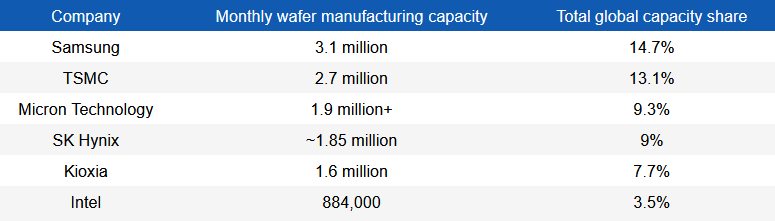

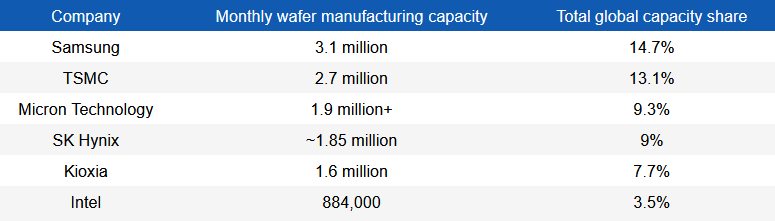

据IC Insights报道,2020年12月期间,前五大晶圆制造商的全球产能占比增至54%。你可能会认为台湾半导体制造公司(TSMC)会领先,考虑到它的客户包括AMD、苹果、高通和博通,但这家纯代工厂的月产能却比三星低了约40万片。

三星利润丰厚的内存业务无疑是其夺得第一的重要原因,而NVIDIA则在其消费级安培产品线上使用了三星8nm工艺的定制版,在A100加速器上坚持使用台积电及其7nm FinFET工艺。

紧随台积电之后,产能排名第三的是美光科技,其月产能超过190万片。SK海力士排名第四(约185万片),然后是存储器IC供应商Kioxia排名第五(160万片)。英特尔拥有自己的制造厂,以每月88.4万片晶圆排在第六位。

芯片短缺所造成的问题是有据可查的,影响的行业包括PC硬件、汽车和游戏机--甚至连拜登政府也参与其中希望解决这一问题。

01

台积电3nm工艺或于2年内准备就绪

台积电董事长刘德音(Dr. Mark Liu)证实,该公司的下一代 3nm 芯片制造节点,正在按计划推进之中。作为全球知名的芯片代工制造商,台积电当前正在建设 3nm 生产线,且有望明年转入试生产。与 5nm 制程节点相比,3nm 可提供几乎翻番的逻辑密度,辅以 11% 的性能提升、或 27% 的能效改进。

3nm较5nm制程的增益示例(图 via WCCFTech)

积电高管在早前的国际固态电路会议(ISSCC)演讲期间的这番表态,证实了该公司对下一代制造技术的信心。

在满足当前和未来产品的日益增长需求的同时,即便汽车领域的产品需求有所提升,也不会对整体产能造成太大影响。

需要指出的是,部分媒体误解了所谓的“3nm 工艺提前”。毕竟在主题为《释放创新未来》的 27 分钟演讲期间,高管并未直言此事,仅在开头和结尾对 3nm 开发进度“顺口一提”。

为提升逻辑密度,需要对相关技术展开协同优化,同时也增加了一定的成本。

除了透露 3nm 技术的发展正在如期推进且相当顺利,刘德音还提供了对 3nm 工艺的最新数据、以及对工艺发展的看法。

他指出,到目前为止,台积电已出货约 18 亿片基于 7nm 工艺节点的芯片。截止 2020 年,该公司一直是行业中的领跑者。

得益于极紫外光刻(EUV)技术,台积电能够实现更高的保真度、缩短周期、并降低工艺的复杂性和缺陷率。

值得一提的是,台积电在 5nm 节点的十层掩模工艺中使用了 EUV 技术(具体包括线切割、接触、金属线图案),并用单层 EUV 取代了早期的多层深紫外(DUV)工艺。

随后刘德音强调了设计技术的协同优化(DTC),以及该方案在过去几年中对芯片制造的重要性。对于芯片制造商来说,这使得他们能够同时使用设计和制造技术来满足性能要求。

此外 DTCO 使得台积电在衡量节点的逻辑密度时超越了固有的缩放指标,比如接触栅间距和最小金属间距。

结合有源区上的栅极接触、单扩散中断、鳍片减少等特性,还可为 3nm 工艺节点带来 1.8 倍于 5nm 的逻辑密度。

最后,刘德音披露了公司的未来计划,包括开发 sub-3D 材料和晶圆级单晶六方氮化硼。

两者的特点是能够在较低的制造温度下,转移至任意衬底上,从而为在三个维度上制造有源逻辑层和存储层开辟了新的道路。

此外台积电对于低维材料的研究,包包括一维的碳纳米管。借助这一晶体通道的关键,是开发出一种栅极长度较短的晶体管介电材料。

如上图所示,研究表明这项技术已有实现的可能。具有高k栅极堆叠能力的新材料,很适合用于制造栅极长度为 10nm 的晶体管。

当然,为了达成如此远大的目标,台积电还需要与芯片行业的所有同行紧密合作,以确保 3nm 工艺能够发展到 2 倍于当前的性能。

考虑到该公司正在量产的 5nm 顺应了这一趋势,即将面世的 3nm 节点也有望遵循这一时间安排。

02

三星去年12月领先台积电

台积电如此积极地推动技术革新,恐怕与三星去年12月领先台积电成为全球头号晶圆制造商有关。

据IC Insights报道,2020年12月期间,前五大晶圆制造商的全球产能占比增至54%。你可能会认为台湾半导体制造公司(TSMC)会领先,考虑到它的客户包括AMD、苹果、高通和博通,但这家纯代工厂的月产能却比三星低了约40万片。

三星利润丰厚的内存业务无疑是其夺得第一的重要原因,而NVIDIA则在其消费级安培产品线上使用了三星8nm工艺的定制版,在A100加速器上坚持使用台积电及其7nm FinFET工艺。

紧随台积电之后,产能排名第三的是美光科技,其月产能超过190万片。SK海力士排名第四(约185万片),然后是存储器IC供应商Kioxia排名第五(160万片)。英特尔拥有自己的制造厂,以每月88.4万片晶圆排在第六位。

芯片短缺所造成的问题是有据可查的,影响的行业包括PC硬件、汽车和游戏机--甚至连拜登政府也参与其中希望解决这一问题。

报纸客服电话:4006677866 报纸客服信箱:pcw-advice@vip.sin*.c*m 友情链接与合作:987349267(QQ) 广告与活动:675009(QQ) 网站联系信箱:cpcw@cpcwi.com

Copyright © 2006-2011 电脑报官方网站 版权所有 渝ICP备10009040号